# Computer Structure & & Introduction to Digital Computers Lecture Notes

by

Guy Even

Dept. of Electrical Engineering - Systems, Tel-Aviv University. Spring 2003

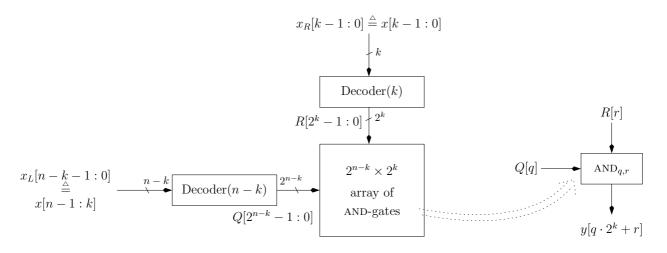

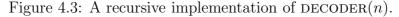

Copyright 2003 by Guy Even Send comments to: guy@eng.tau.ac.il

# Contents

| 1        | The  | e digital abstraction                                                                                        | 1  |  |  |  |  |  |

|----------|------|--------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|

|          | 1.1  | Transistors                                                                                                  | 1  |  |  |  |  |  |

|          | 1.2  | From analog signals to digital signals                                                                       | 3  |  |  |  |  |  |

|          | 1.3  | Transfer functions of gates                                                                                  | 5  |  |  |  |  |  |

|          | 1.4  | The bounded-noise model                                                                                      | 6  |  |  |  |  |  |

|          | 1.5  | The digital abstraction in presence of noise                                                                 | 7  |  |  |  |  |  |

|          |      | 1.5.1 Redefining the digital interpretation of analog signals                                                | 7  |  |  |  |  |  |

|          | 1.6  | Stable signals                                                                                               | 9  |  |  |  |  |  |

|          | 1.7  | Summary                                                                                                      | 10 |  |  |  |  |  |

| <b>2</b> | Fou  | Foundations of combinational circuits 11                                                                     |    |  |  |  |  |  |

|          | 2.1  | Boolean functions                                                                                            | 11 |  |  |  |  |  |

|          | 2.2  | Gates as implementations of Boolean functions                                                                | 11 |  |  |  |  |  |

|          | 2.3  | Building blocks                                                                                              | 12 |  |  |  |  |  |

|          | 2.4  | Combinational circuits                                                                                       | 14 |  |  |  |  |  |

|          | 2.5  | Cost and propagation delay                                                                                   | 18 |  |  |  |  |  |

|          | 2.6  | Syntax and semantics                                                                                         | 19 |  |  |  |  |  |

|          | 2.7  | Summary                                                                                                      | 20 |  |  |  |  |  |

| 3        | Tree | es                                                                                                           | 21 |  |  |  |  |  |

|          | 3.1  | Trees of associative Boolean gates                                                                           | 21 |  |  |  |  |  |

|          |      | 3.1.1 Associative Boolean functions                                                                          | 21 |  |  |  |  |  |

|          |      | 3.1.2 OR-trees                                                                                               | 22 |  |  |  |  |  |

|          |      | 3.1.3 Cost and delay analysis                                                                                | 23 |  |  |  |  |  |

|          | 3.2  | Optimality of trees                                                                                          | 25 |  |  |  |  |  |

|          |      | 3.2.1 Definitions $\ldots$  | 25 |  |  |  |  |  |

|          |      | 3.2.2 Lower bounds $\ldots$ | 26 |  |  |  |  |  |

|          | 3.3  | Summary                                                                                                      | 29 |  |  |  |  |  |

| 4        | Dec  | oders and Encoders                                                                                           | 31 |  |  |  |  |  |

|          | 4.1  | Notation                                                                                                     | 31 |  |  |  |  |  |

|          | 4.2  | Values represented by binary strings                                                                         | 33 |  |  |  |  |  |

|          | 4.3  | Decoders                                                                                                     | 34 |  |  |  |  |  |

|          |      | 4.3.1 Brute force design                                                                                     | 34 |  |  |  |  |  |

|          |      | 4.3.2 An optimal decoder design                                                                              | 35 |  |  |  |  |  |

|          |      | 4.3.3 Correctness                                                                                                                                                                   | 5  |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|          |      | 4.3.4 Cost and delay analysis                                                                                                                                                       | 6  |

|          | 4.4  | Encoders                                                                                                                                                                            | 57 |

|          |      | 4.4.1 Implementation                                                                                                                                                                | 8  |

|          |      | 4.4.2 Cost and delay analysis                                                                                                                                                       | 1  |

|          |      | 4.4.3 Yet another encoder                                                                                                                                                           | 2  |

|          | 4.5  | Summary                                                                                                                                                                             |    |

|          |      | •                                                                                                                                                                                   |    |

| <b>5</b> |      | abinational modules 4'                                                                                                                                                              |    |

|          | 5.1  | Multiplexers                                                                                                                                                                        | -  |

|          |      | 5.1.1 Implementation $\ldots \ldots 4$                                                                        | -  |

|          | 5.2  | Cyclic Shifters                                                                                                                                                                     | -  |

|          |      | 5.2.1 Implementation $\ldots \ldots 5$                                                   |    |

|          | 5.3  | Priority Encoders                                                                                                                                                                   |    |

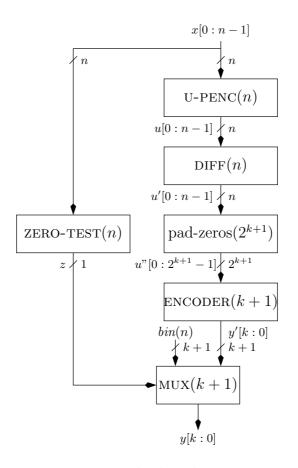

|          |      | 5.3.1 Implementation of U-PENC $(n)$                                                                                                                                                | 4  |

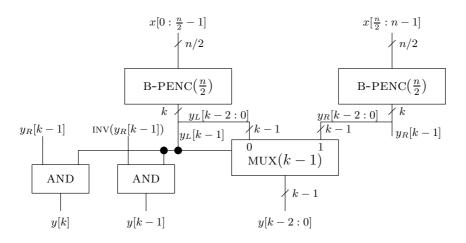

|          |      | 5.3.2 Implementation of B-PENC                                                                                                                                                      | 5  |

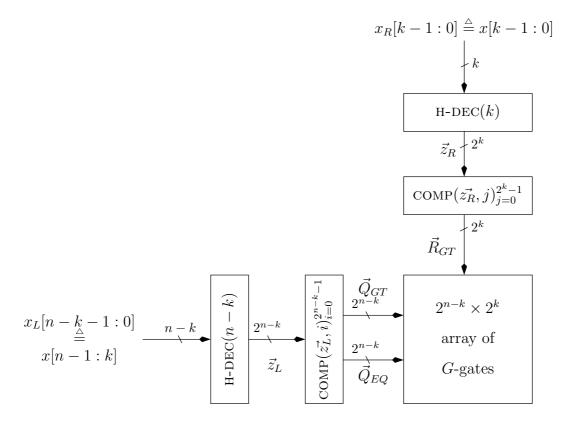

|          | 5.4  | Half-Decoders                                                                                                                                                                       | 9  |

|          |      | 5.4.1 Preliminaries                                                                                                                                                                 | 9  |

|          |      | 5.4.2 Implementation                                                                                                                                                                | 60 |

|          |      | 5.4.3 Correctness                                                                                                                                                                   | 52 |

|          |      | 5.4.4 Cost and delay analysis                                                                                                                                                       | 52 |

|          | 5.5  | Logical Shifters                                                                                                                                                                    | 53 |

|          | 5.6  | Summary                                                                                                                                                                             |    |

|          |      |                                                                                                                                                                                     |    |

| 6        | Add  | lition 64                                                                                                                                                                           | 5  |

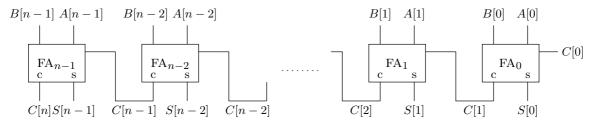

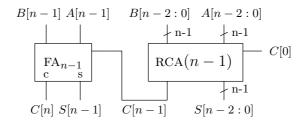

|          | 6.1  | Definition of a binary adder                                                                                                                                                        | 5  |

|          | 6.2  | Ripple Carry Adder    6                                                                                                                                                             | 6  |

|          |      | 6.2.1 Correctness proof                                                                                                                                                             | 6  |

|          |      | 6.2.2 Delay and cost analysis                                                                                                                                                       | 7  |

|          | 6.3  | Carry bits                                                                                                                                                                          | 57 |

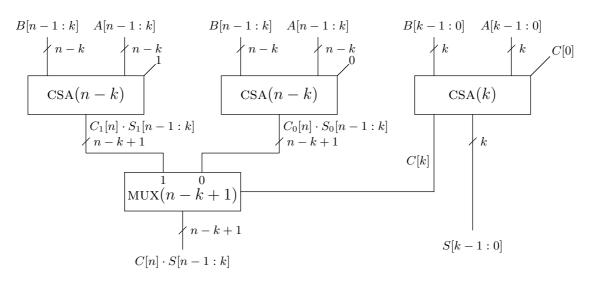

|          | 6.4  | Conditional Sum Adder                                                                                                                                                               | 59 |

|          |      | 6.4.1 Motivation                                                                                                                                                                    | 59 |

|          |      | 6.4.2 Implementation                                                                                                                                                                | 69 |

|          |      | 6.4.3 Delay and cost analysis                                                                                                                                                       | ;9 |

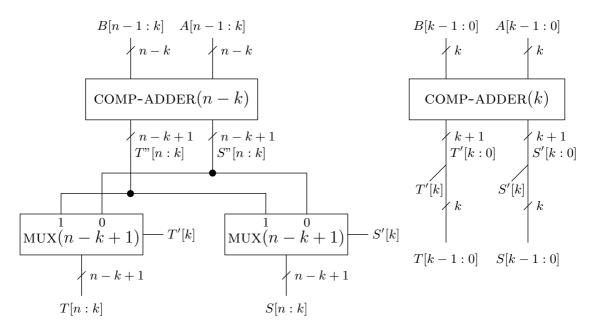

|          | 6.5  | Compound Adder                                                                                                                                                                      |    |

|          |      | 6.5.1 Implementation                                                                                                                                                                |    |

|          |      | 6.5.2 Correctness                                                                                                                                                                   |    |

|          |      | 6.5.3 Delay and cost analysis                                                                                                                                                       |    |

|          | 6.6  | Summary                                                                                                                                                                             |    |

|          | 0.0  |                                                                                                                                                                                     | т  |

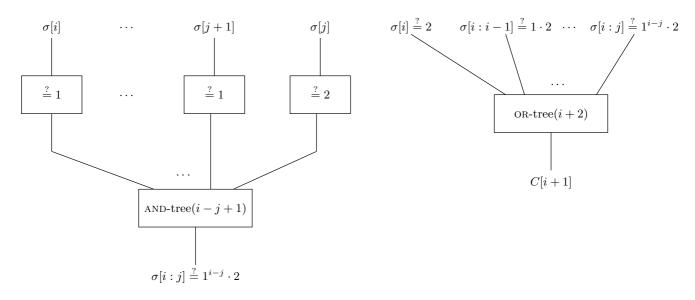

| <b>7</b> | Fast | Addition 73                                                                                                                                                                         | 5  |

|          | 7.1  | Reduction: sum-bits $\longmapsto$ carry-bits $\ldots \ldots \ldots$ | 5  |

|          | 7.2  | Computing the carry-bits                                                                                                                                                            | 5  |

|          |      | 7.2.1 Carry-Lookahead Adders                                                                                                                                                        | 6  |

|          |      | 7.2.2 Reduction to prefix computation                                                                                                                                               | '9 |

|          |      |                                                                                                                                                                                     |    |

|    | 7.3          | Parallel prefix computation817.3.1 Implementation817.3.2 Correctness827.3.3 Delay and cost analysis82 |

|----|--------------|-------------------------------------------------------------------------------------------------------|

|    | $7.4 \\ 7.5$ | Putting it all together    83      Summary    84                                                      |

| 8  | Sign         | ed Addition 85                                                                                        |

|    | 8.1          | Representation of negative integers                                                                   |

|    | 8.2          | Negation in two's complement representation                                                           |

|    | 8.3          | Properties of two's complement representation                                                         |

|    | 8.4          | Reduction: two's complement addition to binary addition                                               |

|    |              | 8.4.1 Detecting overflow                                                                              |

|    |              | 8.4.2 Determining the sign of the sum                                                                 |

|    | 8.5          | A two's-complement adder                                                                              |

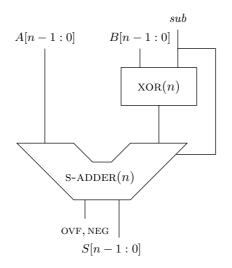

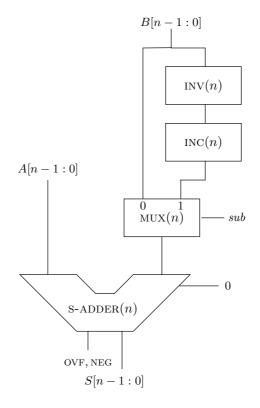

|    | 8.6          | A two's complement adder/subtracter                                                                   |

|    | 8.7          | Additional questions                                                                                  |

|    | 8.8          | Summary                                                                                               |

|    |              |                                                                                                       |

| 9  | Flip         | -Flops 99                                                                                             |

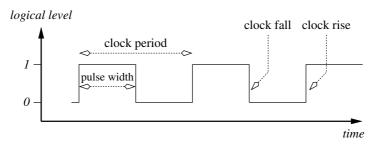

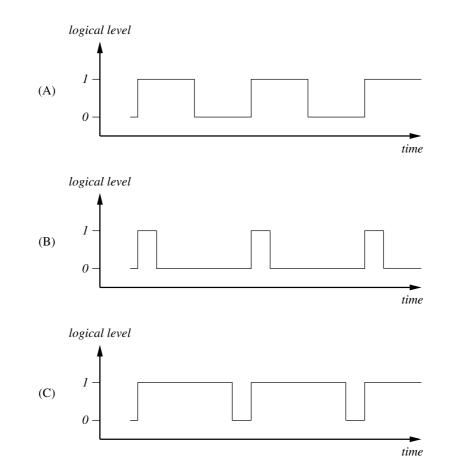

|    | 9.1          | The clock                                                                                             |

|    | 9.2          | Edge-triggered Flip-Flop                                                                              |

|    | 9.3          | Arbitration                                                                                           |

|    | 9.4          | Arbiters - an impossibility result                                                                    |

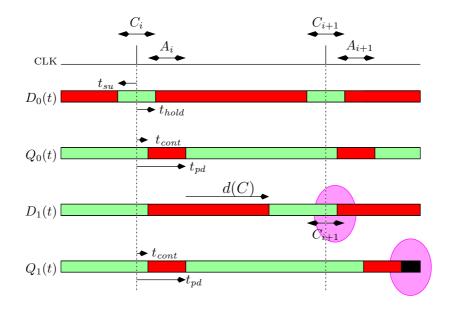

|    | 9.5          | Necessity of critical segments                                                                        |

|    | 9.6          | An example                                                                                            |

|    |              | 9.6.1 Non-empty intersection of $C_i$ and $A_i$                                                       |

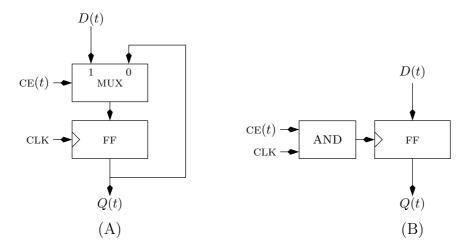

|    | 9.7          | Other types of memory devices                                                                         |

|    |              | 9.7.1 D-Latch                                                                                         |

|    |              | 9.7.2 Clock enabled flip-flips                                                                        |

|    |              |                                                                                                       |

| 10 | Syn          | chronous Circuits 111                                                                                 |

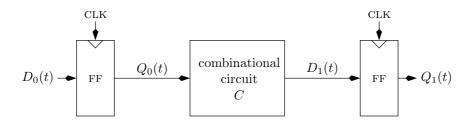

|    | 10.1         | Syntactic definition                                                                                  |

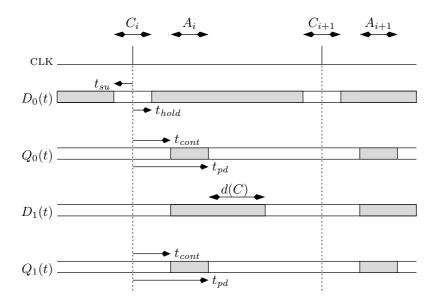

|    | 10.2         | Timing analysis: the canonic form                                                                     |

|    |              | 10.2.1 Canonic form of a synchronous circuit                                                          |

|    |              | 10.2.2 Timing constraints 113                                                                         |

|    |              | 10.2.3 Sufficient conditions                                                                          |

|    |              | 10.2.4 Satisfying the timing constraints                                                              |

|    |              | 10.2.5 Minimum clock period                                                                           |

|    |              | 10.2.6 Initialization                                                                                 |

|    |              | 10.2.7 Functionality                                                                                  |

|    | 10.3         | Timing analysis: the general case                                                                     |

|    | 10.0         | 10.3.1 Timing constraints                                                                             |

|    |              | 10.3.2 Algorithm: minimum clock period                                                                |

|    |              | 10.3.3 Algorithm: correctness                                                                         |

|    |              | 10.0.0 mgorumn. concerness                                                                            |

| 10.3.4 Algorithm: feasibility of timing constraints                                                          | 124 |

|--------------------------------------------------------------------------------------------------------------|-----|

| 10.4 Functionality $\ldots$ | 124 |

| 10.4.1 The zero delay model                                                                                  | 125 |

| 10.4.2 Simulation $\ldots$  | 125 |

| 10.5 Summary                                                                                                 | 125 |

# Chapter 1 The digital abstraction

The term a *digital circuit* refers to a device that works in a binary world. In the binary world, the only values are zeros and ones. Hence, the inputs of a digital circuit are zeros and ones, and the outputs of a digital circuit are zeros and ones. Digital circuits are usually implemented by *electronic devices* and operate in the *real* world. In the real world, there are no zeros and ones; instead, what matters is the voltages of inputs and outputs. Since voltages refer to energy, they are continuous<sup>1</sup>. So we have a gap between the continuous real world and the two-valued binary world. One should not regard this gap as an absurd. Digital circuits are only an *abstraction* of electronic devices. In this chapter we explain this abstraction, called the *digital abstraction*.

In the digital abstraction one interprets voltage values as binary values. The advantages of the digital model cannot be overstated; this model enables one to focus on the digital behavior of a circuit, to ignore analog and transient phenomena, and to easily build larger more complex circuits out of small circuits. The digital model together with a simple set of rules, called *design rules*, enable logic designers to design complex digital circuits consisting of millions of gates.

## 1.1 Transistors

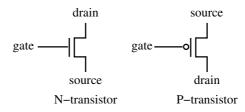

Electronic circuits that are used to build computers are mostly build of *transistors*. Small circuits, called *gates* are built from transistors. The most common technology used in VLSI chips today is called CMOS, and in this technology there are only two types of transistors: N-type and P-type. Each transistor has three connections to the outer world, called the *gate*, *source*, and *drain*. Figure 1.1 depicts diagrams describing these transistors.

Although inaccurate, we will refer, for the sake of simplicity, to the gate and source as inputs and to the drain as an output. An overly simple explanation of an N-type transistor in CMOS technology is as follows: If the voltage of the gate is high (i.e. above some threshold  $v_1$ ), then there is little resistance between the source and the drain. Such a small resistance causes the voltage of the drain to equal the voltage of the source. If the voltage of the gate is low (i.e. below some threshold  $v_0 < v_1$ ), then there is a very high resistance between the

<sup>&</sup>lt;sup>1</sup>unless Quantum Physics is used.

Figure 1.1: Schematic symbols of an N-transistor and P-transistor

source and the drain. Such a high resistance means that the voltage of the drain is unchanged by the transistor (it could be changed by another transistor if the drains of the two transistors are connected). A P-type transistor is behaves in a dual manner: the resistance between drain and the source is low if the gate voltage is below  $v_0$ . If the voltage of the gate is above  $v_1$ , then the source-to-drain resistance is very high.

Note that this description of transistor behavior implies immediately that transistors are highly non-linear. (Recall that a linear function f(x) satisfies  $f(a \cdot x) = a \cdot f(x)$ .) In transistors, changes of 10% in input values above the threshold  $v_1$  have a small effect on the output while changes of 10% in input values between  $v_0$  and  $v_1$  have a large effect on the output. In particular, this means that transistors do not follow Ohm's Law (i.e.  $V = I \cdot R$ ).

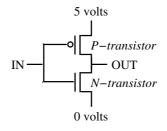

**Example 1.1 (A CMOS inverter)** Figure 1.2 depicts a CMOS inverter. If the input voltage is above  $v_1$ , then the source-to-drain resistance in the P-transistor is very high and the source-to-drain resistance in the N-transistor is very low. Since the source of the N-transistor is connected to low voltage (i.e. ground), the output of the inverter is low.

If the input voltage is below  $v_0$ , then the source-to-drain resistance in the N-transistor is very high and the source-to-drain resistance in the P-transistor is very low. Since the source of the P-transistor is connected to high voltage, the output of the inverter is high.

We conclude that the voltage of the output is low when the input is high, and vice-versa, and the device is indeed an inverter.

Figure 1.2: A CMOS inverter

The qualitative description in Example 1.1 hopefully conveys some intuition about how gates are built from transistors. A quantitative analysis of such an inverter requires precise modeling of the functionality of the transistors in order to derive the input-output voltage relation. One usually performs such an analysis by computer programs (e.g. SPICE). Quantitative analysis is relatively complex and inadequate for designing large systems like computers. (This would be like having to deal with the chemistry of ink when using a pen.)

## **1.2** From analog signals to digital signals

An analog signal is a real function  $f : \mathbb{R} \to \mathbb{R}$  that describes the voltage of a given point in a circuit as a function of the time. We ignore the resistance and capacities of wires. Moreover, we assume that signals propagate through wires immediately<sup>2</sup>. Under these assumptions, it follows that the voltage along a wire is identical at all times. Since a signal describes the voltage (i.e. derivative of energy as a function of electric charge), we also assume that a signal is a continuous function.

A digital signal is a function  $g : \mathbb{R} \to \{0, 1, \text{non-logical}\}$ . The value of a digital signal describes the logical value carried along a wire as a function of time. To be precise there are two logical values: zero and one. The non-logical value simply means that the signal is neither zero or one.

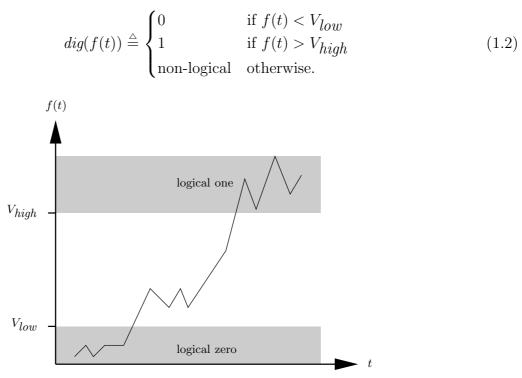

How does one interpret an analog signal as a digital signal? The simplest interpretation is to set a threshold V'. Given an analog signal f(t), the digital signal dig(f(t)) can be defined as follows.

$$dig(f(t)) \triangleq \begin{cases} 0 & \text{if } f(t) < V' \\ 1 & \text{if } f(t) > V' \end{cases}$$

(1.1)

According to this definition, a digital interpretation of an analog signal is always 0 or 1, and the digital interpretation is never non-logical.

There are several problems with the definition in Equation 1.1. One problem with this definition is that all the components should comply with *exactly* the same threshold V'. In reality, devices are not completely identical; the actual thresholds of different devices vary according to a tolerance specified by the manufacturer. This means that instead of a fixed threshold, we should consider a range of thresholds.

Another problem with the definition in Equation 1.1 is caused by perturbations of f(t)around the threshold t. Such perturbations can be caused by *noise* or oscillations of f(t)before it stabilizes. We will elaborate more on noise later, and now explain why oscillations can occur. Consider a spring connected to the ceiling with a weight w hanging from it. We expect the spring to reach a length  $\ell$  that is proportional to the weight w. Assume that all we wish to know is whether the length  $\ell$  is greater than a threshold  $\ell_t$ . Sounds simple! But what if  $\ell$  is rather close to  $\ell_t$ ? In practice, the length only tends to the length  $\ell$  as time progresses; the actual length of the spring oscillates around  $\ell$  with a diminishing amplitude. Hence, the length of the spring fluctuates below and above  $\ell_t$  many times before we can decide. This effect may force us to wait for a long time before we can decide if  $\ell < \ell_t$ . If we return to the definition of dig(f(t)), it may well happen that f(t) oscillates around the threshold V'. This renders the digital interpretation used in Eq. 1.1 useless.

Returning to the example of weighing weights, assume that we have two types of objects: light and heavy. The weight of a light (resp., heavy) object is at most (resp., at least)  $w_0$ (resp.,  $w_1$ ). The bigger the gap  $w_1 - w_0$ , the easier it becomes to determine if an object is light or heavy (especially in the presence of noise or oscillations).

Now we have two reasons to introduce two threshold values instead of one, namely, different threshold values for different devices and the desire to have a gap between values

<sup>&</sup>lt;sup>2</sup>This is a reasonable assumption if wires are short.

interpreted as logical zero and logical one. We denote these thresholds by  $V_{low}$  and  $V_{high}$ , and require that  $V_{low} < V_{high}$ . An interpretation of an analog signal is depicted in Figure 1.3. Consider an analog signal f(t). The digital signal dig(f(t)) is defined as follows.

Figure 1.3: A digital interpretation of an analog signal in the zero-noise model.

We often refer to the logical value of an analog signal f. This is simply a shorthand way of referring to the value of the digital signal dig(f).

It is important to note that fluctuations of f(t) are still possible around the threshold values. However, if the two thresholds are sufficiently far away from each other, fluctuations of f do not cause fluctuations of dig(f(t)) between 0 and 1. Instead, we will have at worst fluctuations of dig(f(t)) between a non-logical value and a logical value (i.e. 0 or 1). A fluctuation between a logical value and a non-logical value is much more favorable than a fluctuation between 0 and 1. The reason is that a non-logical value is an indication that the circuit is still in a transient state and a "decision" has not been reached yet.

Assume that we design an inverter so that its output tends to a voltage that is bounded away from the thresholds  $V_{low}$  and  $V_{high}$ . Let us return to the example of the spring with weight w hanging from it. Additional fluctuations in the length of the spring might be caused by wind. This means that we need to consider additional effects so that our model will be useful. In the case of the digital abstraction, we need to take *noise* into account. Before we consider the effect of noise, we formulate the static functionality of a gate, namely, the values of its output as a function of its stable inputs.

**Question 1.1** Try to define an inverter in terms of the voltage of the output as a function of the voltage of the input.

## **1.3** Transfer functions of gates

The voltage at an output of a gate depends on the voltages of the inputs of the gate. This dependence is called the *transfer function* (or the *voltage-transfer characteristic* - VTC). Consider, for example an inverter with an input x and an output y. To make things complicated, the value of the signal y(t) at time t is not only a function of the signal x at time t since y(t) depends on the history. Namely,  $y(t_0)$  is a function of x(t) over the interval  $(-\infty, t_0]$ .

Transfer functions are solved by modeling gates with partial differential equations, a rather complicated task. A good approximation of transfer functions is obtain by solving differential equations, still a complicated task that can be computed quickly only for a few transistors. So how are chips that contain millions of chips designed?

The way this very intricate problem is handled is by restricting designs. In particular, only a small set of building blocks is used. The building blocks are analyzed intensively, their properties are summarized, and designers rely on these properties for their designs.

One of the most important steps in characterizing the behavior of a gate is computing its static transfer function. Returning to the example of the inverter, a "proper" inverter has a unique output value point for each input value. Namely, if the input x(t) is stable for a sufficiently long period of time and equals  $x_0$ , then the output y(t) stabilizes on a value  $y_0$ that is a function of  $x_0$ .<sup>3</sup> We formalize the definition of a static transfer function of a gate G with one input x and one output y in the following definition.

**Definition 1.1** Consider a device G with one input x and one output y. The device G is a gate if its functionality is specified by a function  $f : \mathbb{R} \to \mathbb{R}$  as follows: there exists a  $\Delta > 0$ , such that, for every  $x_0$  and every  $t_0$ , if  $x(t) = x_0$  for every  $t \in [t_0 - \Delta, t_0]$ , then  $y(t_0) = f(x_0)$ . Such a function f(x) is called the static transfer function of G.

At this point we should point the following remarks:

- 1. Since circuits operate over a bounded range of voltages, static transfer functions are usually only defined over bounded domains and ranges (say [0, 5] volts).

- 2. To make the definition useful, one should allow perturbations of x(t) during the interval  $[t_0 \Delta, t_0]$ . Static transfer functions model physical devices, and hence, are continuous. This implies the following definition: For every  $\epsilon > 0$ , there exist a  $\delta > 0$  and a  $\Delta > 0$ , such that

$$\forall t \in [t_1, t_2] : |x(t) - x_0| \le \delta \quad \Rightarrow \quad \forall t \in [t_1 + \Delta, t_2] : |y(t) - f(x_0)| \le \epsilon$$

<sup>&</sup>lt;sup>3</sup>If this were not the case, then we need to distinguish between two cases: (a) Stability is not reached: this case occurs, for example, with devices called oscillators. Note that such devices must consume energy even when the input is stable. We point out that in CMOS technology it is easy to design circuits that do not consume energy if the input is logical, so such oscillations are avoided. (b) Stability is reached: in this case, if there is more than one stable output value, it means that the device has more than one equilibrium point. Such a device can be used to store information about the "history". It is important to note that devices with multiple equilibriums are very useful as storage devices (i.e. they can "remember" a small amount of information). Nevertheless, devices with multiple equilibriums are not "good" candidates for gates, and it is easy to avoid such devices in CMOS technology.

3. Note that in the above definition  $\Delta$  does not depend on  $x_0$  (although it may depend on  $\epsilon$ ). Typically, we are interested on the values of  $\Delta$  only for logical values of x(t) (i.e.  $x(t) \leq V_{low}$  and  $x(t) \geq V_{high}$ ). Once the value of  $\epsilon$  is fixed, this constant  $\Delta$  is called the *propagation delay* of the gate G and is one of the most important characteristic of a gate.

#### **Question 1.2** Extend Definition 1.1 to gates with n inputs and m outputs.

Finally, we can now define an inverter in the zero-noise model. Observe that according to this definition a device is an inverter if its static transfer function satisfies a certain property.

**Definition 1.2 (inverter in zero-noise model)** A gate G with a single input x and a single output y is an inverter if its static transfer function f(z) satisfies the following the following two conditions:

1. If

$$z < V_{\text{low}}$$

, then  $f(z) > V_{\text{high}}$ .

2. If  $z > V_{\text{high}}$ , then  $f(z) < V_{\text{low}}$ .

The implication of this definition is that if the logical value of the input x is zero (resp., one) during an interval  $[t_1, t_2]$  of length at least  $\Delta$ , then the logical value of the output y is one (resp., zero) during the interval  $[t_1 + \Delta, t_2]$ .

How should we define other gates such a NAND-gates, XOR-gates, etc.? As in the definition of an inverter, the definition of a NAND-gate is simply a property of its static transfer function.

Question 1.3 Define a NAND-gate.

We are now ready to strengthen the digital abstraction so that it will be useful also in the presence of bounded noise.

#### 1.4 The bounded-noise model

Consider a wire from point A to point B. Let A(t) (resp., B(t)) denote the analog signal measured at point A (resp., B). We would like to assume that wires have zero resistance, zero capacitance, and that signals propagate through a wire with zero delay. This assumption means that the signals A(t) and B(t) should be equal at all times. Unfortunately, this is not the case; the main reason for this discrepancy is *noise*.

There are many sources of noise. The main source is heat that causes electrons to move randomly. These random movements do not cancel out perfectly, and random currents are created. These random currents create perturbations in the voltage of a wire. The difference between the signals B(t) and A(t) is a noise signal.

Consider, for example, the setting of *additive noise*: A is an output of an inverter and B is an input of another inverter. We consider the signal A(t) to be a reference signal. The signal B(t) is the sum  $A(t) + n_B(t)$ , where  $n_B(t)$  is the noise signal.

#### 1.5. THE DIGITAL ABSTRACTION IN PRESENCE OF NOISE

The bounded-noise model assumes that the noise signal along every wire has a bounded absolute value. We will use a slightly simplified model in which there is a constant  $\epsilon > 0$ such that the absolute value of all noise signals is bounded by  $\epsilon$ . We refer to this model as the uniform bounded noise model. The justification for assuming that noise is bounded is probabilistic. Noise is a random variable whose distribution has a rapidly diminishing tail. This means that if the bound is sufficiently large, then the probability of the noise exceeding this bound during the lifetime of a circuit is negligibly small.

## **1.5** The digital abstraction in presence of noise

Consider two inverters, where the output of one gate feeds the input of the second gate. Figure 1.4 depicts such a circuit that consists of two inverters.

Assume that the input x has a value that satisfies: (a)  $x > V_{high}$ , so the logical value of x is one, and (b)  $y = V_{low} - \epsilon'$ , for a very small  $\epsilon' > 0$ . This might not be possible with every inverter, but Definition 1.2 does not rule out such an inverter. (Consider a transfer function with  $f(V_{high}) = V_{low}$ , and x slightly higher than  $V_{high}$ .) Since the logical value of y is zero, it follows that the second inverter, if not faulty, should output a value z that is greater than  $V_{high}$ . In other words, we expect the logical value of z to be 1. At this point we consider the effect of adding noise.

Let us denote the noise added to the wire y by  $n_y$ . This means that the input of the second inverter equals  $y(t) + n_y(t)$ . Now, if  $n_y(t) > \epsilon'$ , then the second inverter is fed a non-logical value! This means that we can no longer deduce that the logical value of z is one. We conclude that we must use a more resilient model; in particular, the functionality of circuits should not be affected by noise. Of course, we can only hope to be able to cope with bounded noise, namely noise whose absolute value does not exceed a certain value  $\epsilon$ .

Figure 1.4: Two inverters connected in series.

#### **1.5.1** Redefining the digital interpretation of analog signals

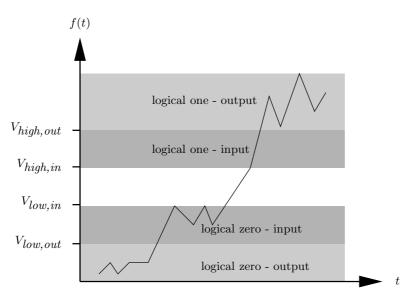

The way we deal with noise is that we interpret input signals and output signals differently. An input signal is a signal measured at an input of a gate. Similarly, an output signal is a signal measured at an output of a gate. Instead of two thresholds,  $V_{low}$  and  $V_{high}$ , we define the following four thresholds:

- $V_{low,in}$  an upper bound on a voltage of an input signal interpreted as a logical zero.

- $V_{low,out}$  an upper bound on a voltage of an output signal interpreted as a logical zero.

- $V_{high.in}$  a lower bound on a voltage of an input signal interpreted as a logical one.

- $V_{high,out}$  a lower bound on a voltage of an output signal interpreted as a logical one.

These four thresholds satisfy the following equation:

$$V_{low,out} < V_{low,in} < V_{high,in} < V_{high,out}.$$

(1.3)

Figure 1.5 depicts these four thresholds. Note that the interpretation of input signals is less strict than the interpretation of output signals. The actual values of these four thresholds depend on the transfer functions of the devices we wish to use.

The differences  $V_{low,in} - V_{low,out}$  and  $V_{high,out} - V_{high,in}$  are called *noise margins*. Our goal is to show that noise whose absolute value is less than the noise margin will not change the logical value of an output signal. Indeed, if the absolute value of the noise n(t) is bounded by the noise margins, then an output signal  $f_{out}(t)$  that is below  $V_{low,out}$  will result with an input signal  $f_{in}(t) = f_{out}(t) + n(t)$  that does not exceed  $V_{low,in}$ .

Figure 1.5: A digital interpretation of an input and output signals.

Consider an input signal  $f_{in}(t)$ . The digital signal  $dig(f_{in}(t))$  is defined as follows.

$$dig(f_{in}(t)) \triangleq \begin{cases} 0 & \text{if } f_{in}(t) < V_{low,in} \\ 1 & \text{if } f_{in}(t) > V_{high,in} \\ \text{non-logical otherwise.} \end{cases}$$

(1.4)

Consider an output signal  $f_{out}(t)$ . The digital signal  $dig(f_{out}(t))$  is defined analogously.

$$dig(f_{out}(t)) \triangleq \begin{cases} 0 & \text{if } f_{out}(t) < V_{low,out} \\ 1 & \text{if } f_{out}(t) > V_{high,out} \\ \text{non-logical otherwise.} \end{cases}$$

(1.5)

#### 1.6. STABLE SIGNALS

Observe that sufficiently large noise margins imply that noise will not change the logical values of signals.

We can now fix the definition of an inverter so that bounded noise added to outputs, does not affect logical interpretation of signals.

**Definition 1.3 (inverter in the bounded-noise model)** A gate G with a single input x and a single output y is an inverter if its static transfer function f(z) satisfies the following the following two conditions:

1. If  $z < V_{\text{low,in}}$ , then  $f(z) > V_{\text{high,out}}$ .

2. If  $z > V_{\text{high,in}}$ , then  $f(z) < V_{\text{low,out}}$ .

Question 1.4 Define a NAND-gate in the bounded-noise model.

Question 1.5 Consider the function f(x) = 1 - x over the interval [0,1]. Suppose that f(x) is a the transfer function of a device C. Can you define threshold values  $V_{\text{low,out}} < V_{\text{low,in}} < V_{\text{high,in}} < V_{\text{high,out}}$  so that C is an inverter according to Definition 1.3?

**Question 1.6** Consider a function  $f : [0,1] \rightarrow [0,1]$ . Suppose that: (i) f(0) = 1, and f(1) = 0, (ii) f(x) is monotone decreasing, (iii) the derivative f'(x) of f(x) satisfies the following conditions: f'(x) is continuous and there is an interval  $(\alpha, \beta)$  such that f'(x) < -1 for every  $x \in (\alpha, \beta)$ . And, (iv) there exists a point  $x_0 \in (\alpha, \beta)$  such that  $f(x_0) = x_0$ .

Prove that one can define threshold values  $V_{\text{low,out}} < V_{\text{low,in}} < V_{\text{high,in}} < V_{\text{high,out}}$ so that C is an inverter according to Definition 1.3?

*Hint:* consider a  $\delta > 0$  and set  $V_{\text{low,in}} = x_0 - \delta$  and  $V_{\text{high,in}} = x_0 + \delta$ . What is the largest value of  $\delta$  one can use?

**Question 1.7** Try to characterize transfer functions g(x) that correspond to inverters. Namely, if  $C_g$  is a device, the transfer function of which equals g(x), then one can define threshold values that satisfy Definition 1.3.

#### 1.6 Stable signals

In this section we define terminology that will be used later. To simplify notation we define these terms in the zero-noise model. We leave it to the curious reader to extend the definitions and notation below to the bounded-noise model.

An analog signal f(t) is said to be *logical at time* t if  $dig(f(t)) \in \{0, 1\}$ . An analog signal f(t) is said to be *stable* during the interval  $[t_1, t_2]$  if f(t) is logical for every  $t \in [t_1, t_2]$ . Continuity of f(t) and the fact that  $V_{low} < V_{high}$  imply the following claim.

**Claim 1.1** If an analog signal f(t) is stable during the interval  $[t_1, t_2]$  then one of the following holds:

1. dig(f(t)) = 0, for every  $t \in [t_1, t_2]$ , or

2.  $\operatorname{dig}(f(t)) = 1$ , for every  $t \in [t_1, t_2]$ .

From this point we will deal with digital signals and use the same terminology. Namely, a digital signal x(t) is *logical* at time t if  $x(t) \in \{0, 1\}$ . A digital signal is *stable* during an interval  $[t_1, t_2]$  if x(t) is logical for every  $t \in [t_1, t_2]$ .

## 1.7 Summary

In this chapter we presented the digital abstraction of analog devices. For this purpose we defined analog signals and their digital counterpart, called digital signals. In the digital abstraction, analog signals are interpreted either as zero, one, or non-logical.

We discussed noise and showed that to make the model useful, one should set stricter requirements from output signals than from input signals. Our discussion is based on the bounded-noise model in which there is an upper bound on the absolute value of noise.

We defined gates using transfer functions and static transfer functions. This functions describe the analog behavior of devices. We also defined the propagation delay of a device as the amount of time that input signals must be stable to guarantee stability of the output of a gate.

# Chapter 2 Foundations of combinational circuits

In this chapter we define and study combinational circuits. Our goal is to prove two theorems: (A) Every Boolean function can be implemented by a combinational circuit, and (B) Every combinational circuit implements a Boolean function.

## 2.1 Boolean functions

Let  $\{0,1\}^n$  denote the set of *n*-bit strings. A Boolean function is defined as follows.

**Definition 2.1** A function  $f: \{0,1\}^n \to \{0,1\}^k$  is called a Boolean function.

## 2.2 Gates as implementations of Boolean functions

A gate is a device that has inputs and outputs. The inputs and outputs of a gate are often referred to as *terminals*, *ports*, or even *pins*. In combinational gates, the relation between the logical values of the outputs and the logical values of the inputs is specified by a Boolean function. It takes some time till the logical values of the outputs of a gate properly reflect the value of the Boolean function. We say that a gate is *consistent* if this relation holds. To simplify notation, we consider a gate G with 2 inputs, denoted by  $x_1, x_2$ , and a single output, denoted by y. We denote the digital signal at terminal  $x_1$  by  $x_1(t)$ . The same notation is used for the other terminals. Consistency is defined formally as follows:

**Definition 2.2** A gate G is consistent with a Boolean function f at time t if the input values are digital at time t and

$$y(t) = f(x_1(t), x_2(t)).$$

The propagation delay is the amount of time that elapses till a gate becomes consistent. The following definition defines when a gate implements a Boolean function with propagation delay  $t_{pd}$ .

**Definition 2.3** A gate G implements a Boolean function  $f : \{0,1\}^2 \to \{0,1\}$  with propagation delay  $t_{pd}$  if the following holds.

For every  $\sigma_1, \sigma_2 \in \{0, 1\}$ , if  $x_i(t) = \sigma_i$ , for i = 1, 2, during the interval  $[t_1, t_2]$ , then

$$\forall t \in [t_1 + t_{pd}, t_2] : y(t) = f(\sigma_1, \sigma_2).$$

The following remarks should be well understood before we continue:

- 1. The above definition can be stated in a more compact form. Namely, a gate G implements a Boolean function  $f : \{0, 1\}^n \to \{0, 1\}$  with propagation delay  $t_{pd}$  if stability of the inputs of G in the interval  $[t_1, t_2]$  implies that the gate G is consistent with f in the interval  $[t_1 + t_{pd}, t_2]$ .

- 2. If  $t_2 < t_1 + t_{pd}$ , then the statement in the above definition is empty. It follows that the inputs of a gate must be stable for at least a period of  $t_{pd}$ , otherwise, the gate need not reach consistency.

- 3. Assume that the gate G is consistent at time  $t_2$ , and that at least one input is not stable in the interval  $(t_2, t_3)$ . We do not assume that the output of G remains stable after  $t_2$ . The contamination delay of a gate is the amount of time that the output of a consistent gate remains stable after its inputs stop being stable. Throughout this course, unless stated otherwise, we will make the most "pessimistic" assumption about the contamination delay. Namely, we will assume that the contamination delay is zero.

- 4. If a gate G implements a Boolean function  $f : \{0, 1\}^n \to \{0, 1\}$  with propagation delay  $t_{pd}$ , then G also implements a Boolean function  $f : \{0, 1\}^n \to \{0, 1\}$  with propagation delay t', for every  $t' \ge t_{pd}$ . It follows that it is legitimate to use upper bounds on the actual propagation delay. Pessimistic assumptions should not render a circuit incorrect.

In fact, the actual exact propagation delay is very hard to compute. It depends on x(t) (i.e how fast does the input change?). This is why we resort to upper bounds on the propagation delays.

#### 2.3 Building blocks

The building blocks of combinational circuits are gates and wires. In fact, we will need to consider *nets* which are generalizations of wires.

**Gates.** A gate, as seen in Definition 2.3 is a device that implements a Boolean function. The *fan-in* of a gate G is the number of inputs terminals of G (i.e. the number of bits in the domain of the Boolean function that specifies the functionality of G). The basic gates that we will be using as building blocks for combinational circuits have a constant fan-in (i.e. at most 2-3 input ports). The basic gates that we consider are: inverter (NOT-gate), OR-gate, NOR-gate, AND-gate, NAND-gate, XOR-gate, NXOR-gate, multiplexer (MUX).

The input ports of a gate G are denoted by the set  $\{in(G)_i\}_{i=1}^n$ , where n denotes the fan-in of G. The output ports of a gate G are denoted by the set  $\{out(G)_i\}_{i=1}^k$ , where k denotes the number of output ports of G.

#### 2.3. BUILDING BLOCKS

Wires and nets. A wire is a connection between two terminals (e.g. an output of one gate and an input of another gate). In the zero-noise model, the signals at both ends of a wire are identical.

Very often we need to connect several terminals (i.e. inputs and outputs of gates) together. We could, of course, use any set of edges (i.e. wires) that connects these terminals together. Instead of specifying how the terminals are physically connected together, we use nets.

#### **Definition 2.4** A net is a subset of terminals that are connected by wires.

In the digital abstraction we assume that the signals all over a net are identical (why?). The *fan-out* of a net N is the number of input terminals that are connected by N.

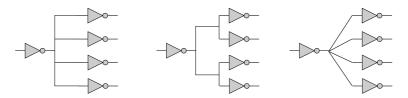

The issue of drawing nets is a bit confusing. Figure 2.1 depicts three different drawings of the same net. All three nets contain an output terminal of an inverter and 4 input terminals of inverters. However, the nets are drawn differently. Recall that the definition of a net is simply a subset of terminals. We may draw a net in any way that we find convenient or aesthetic. The interpretation of the drawing is that terminals that are connected by lines or curves constitute a net.

Figure 2.1: Three equivalent nets.

Consider a net N. We would like to define the digital signal N(t) for the whole net. The problem is that due to noise (and other reasons) the analog signals at different terminals of the net might not equal each other. This might cause the digital interpretations of analog signals at different terminals of the net to be different, too. We solve this problem by defining N(t) to logical only if there is a consensus among all the digital interpretations of analog signals at different terminals of the net. Namely, N(t) is zero (one) if the digital values of all the analog signals along the net are zero (one). If there is no consensus, then N(t) is nonlogical. Recall that, in the bounded-noise model, different thresholds are used to interpret the digital values of the analog signals measured in input and output terminals.

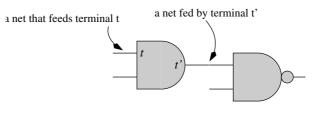

We say that a net N feeds an input terminal t if the input terminal t is in N. We say that a net N is fed by an output terminal t if t is in N. Figure 2.2 depicts an output terminal that feeds a net and an input terminal that is fed by a net. The notion of feeding and being fed implies a direction according to which information "flows"; namely, information is "supplied" by output terminals and is "consumed" by input terminals. From an electronic point of view, in "pure" CMOS gates, output terminals are connected via resistors either to the ground or to the power. Input terminals are connected only to capacitors.

The following definition captures the type of nets we would like to use. We call these nets *simple*.

Figure 2.2: A terminal that is fed by a net and a terminal that feeds a net.

**Definition 2.5** A net N is simple if (a) N is fed by exactly one output terminal, and (b) N feeds at least one input terminal.

A simple net N that is fed by the output terminal t and feeds the input terminals  $\{t_i\}_{i \in I}$ , can be modeled by wires  $\{w_i\}_{i \in I}$ . Each wire  $w_i$  connects t and  $t_i$ . In fact, since information flows in one direction, we may regard each wire  $w_i$  as a directed edge  $t \to t_i$ .

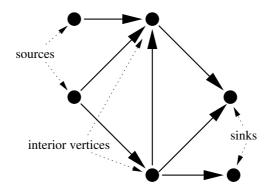

It follows that a circuit, all the nets of which are simple, may be modeled by a directed graph. We define this graph in the following definition.

**Definition 2.6** Let C denote a circuit, all the nets of which are simple. The directed graph DG(C) is defined as follows. The vertices of the graph DG(C) are the gates of C. The directed edges correspond to the wires as follows. Consider a simple net N fed by an output terminal t that feeds the input terminals  $\{t_i\}_{i\in I}$ . The directed edges that correspond to N are  $u \to v_i$ , where u is the gate that contains the output terminal t and  $v_i$  is the gate that contains the input terminal  $t_i$ .

Note that the information of which terminal is connected to each wire is not maintained in the graph DG(C). One could of course label each endpoint of an edge in DG(C) with the name of the terminal the edge is connected to.

## 2.4 Combinational circuits

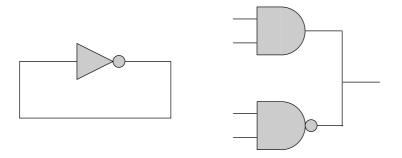

**Question 2.1** Consider the circuits depicted in Figure 2.3. Can you explain why these are not valid combinational circuits?

Before we define combinational circuits it is helpful to define two types of special gates: an input gate and an output gate. The purpose of these gates is to avoid endpoints in nets that seem to be not connected (for example, all the nets in the circuit on the right in Figure 2.3 have endpoints that are not connected to a gate).

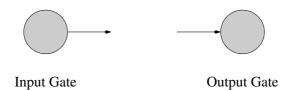

**Definition 2.7 (input and output gates)** An input gate is a gate with zero inputs and a single output. An output gate is a gate with one input and zero outputs.

Figure 2.4 depicts an input gate and an output gate. Inputs from the "external world" are fed to a circuit via input gates. Similarly, outputs to the "external world" are fed by the circuit via output gates.

#### 2.4. COMBINATIONAL CIRCUITS

Figure 2.3: Two examples of non-combinational circuits.

Figure 2.4: An input gate and an output gate

Consider a fixed set of gate-types (e.g. inverter, NAND-gate, etc.); we often refer to such a set of gate-types as a *library*. We associate with every gate-type in the library the number of inputs, the number of outputs, and the Boolean function that specifies its functionality.

Let  $\mathcal{G}$  denote the set of gates in a circuit. Every gate  $G \in \mathcal{G}$  is an *instance* of a gate from the library. Formally, the *gate-type* of a gate G indicates the library element that corresponds to G (e.g. "the gate-type of G is an inverter"). To simplify the discussion, we simply refer to a gate G as an inverter instead of saying that its gate-type is an inverter.

We now present a syntactic definition of combinational circuits.

**Definition 2.8 (syntactic definition of combinational circuits)** A combinational circuit is a pair  $C = \langle \mathcal{G}, \mathcal{N} \rangle$  that satisfies the following conditions:

- 1. G is a set of gates.

- 2.  $\mathcal{N}$  is a set of nets over terminals of gates in  $\mathcal{G}$ .

- 3. Every terminal t of a gate  $G \in \mathcal{G}$  belongs to exactly one net  $N \in \mathcal{N}$ .

- 4. Every net  $N \in \mathcal{N}$  is simple.

- 5. The directed graph DG(C) is acyclic.

Note that Definition 2.8 is independent of the gate types. One need not even know the gatetype of each gate to determine whether a circuit is combinational. Moreover, the question of whether a circuit is combinational is a purely topological question (i.e. are the interconnections between gates legal?). **Question 2.2** Which conditions in the syntactic definition of combinational circuits are violated by the circuits depicted in Figure 2.3?

We list below a few properties that explain why the syntactic definition of combinational circuits is so important. In particular, these properties show that the syntactic definition of combinational circuits implies well defined semantics.

- 1. Completeness: for every Boolean function f, there exists a combinational circuit that implements f. We leave the proof of this property as an exercise for the reader.

- 2. Soundness: every combinational circuit implements a Boolean function. Note that it is NP-Complete to decide if the Boolean function that is implemented by a given combinational circuit with one output ever gets the value 1.

- 3. Simulation: given the digital values of the inputs of a combinational circuit, one can simulate the circuit in linear time. Namely, one can compute the digital values of the outputs of the circuit that are output by the circuit once the circuit becomes consistent.

- 4. Delay analysis: given the propagation delays of all the gates in a combinational circuit, one can compute in linear time an upper bound on the propagation delay of the circuit. Moreover, computing tighter upper bounds is again NP-Complete.

The last three properties are proved in the following theorem by showing that in a combinational circuit every net implements a Boolean function of the inputs of the circuit.

**Theorem 2.1 (Simulation theorem of combinational circuits)** Let  $C = \langle \mathcal{G}, \mathcal{N} \rangle$  denote a combinational circuit that contains k input gates. Let  $\{x_i\}_{i=1}^k$  denote the output terminals of the input gates in C. Assume that the digital signals  $\{x_i(t)\}_{i=1}^k$  are stable during the interval  $[t_1, t_2]$ . Then, for every net  $N \in \mathcal{N}$  there exist:

- 1. a Boolean function  $f_N: \{0,1\}^k \to \{0,1\}$ , and

- 2. a propagation delay  $t_{pd}(N)$

such that

$$N(t) = f_N(x_1(t), x_2(t), \dots, x_k(t)),$$

for every  $t \in [t_1 + t_{pd}(N), t_2]$ .

We can simplify the statement of Theorem 2.1 by considering each net  $N \in \mathcal{N}$  as an output of a combinational circuit with k inputs. The theorem then states that every net implements a Boolean function with an appropriate propagation delay.

We use  $\vec{x}(t)$  to denote the vector  $x_1(t), \ldots, x_k(t)$ .

**Proof:** Let *n* denote the number of gates in  $\mathcal{G}$  and *m* the number of nets in  $\mathcal{N}$ . The directed graph DG(C) is acyclic. It follows that we can topologically sort the vertices of DG(C). Let  $v_1, v_2, \ldots, v_n$  denote the set of gates  $\mathcal{G}$  according to the topological order. (This means that if there is a directed path from  $v_i$  to  $v_j$  in DG(C), then i < j.) We assume, without loss of generality, that  $v_1, \ldots, v_k$  is the set of input gates.

Let  $\mathcal{N}_i$  denote the subset of nets in  $\mathcal{N}$  that are fed by gate  $v_i$ . Note that if  $v_i$  is an output gate, then  $\mathcal{N}_i$  is empty. Let  $e_1, e_2, \ldots, e_m$  denote an ordering of the nets in  $\mathcal{N}$  such that nets in  $\mathcal{N}_i$  precede nets in  $\mathcal{N}_{i+1}$ , for every i < n. In other words, we first list the nets fed by gate  $v_1$ , followed by a list of the nets fed by gate  $v_2$ , etc.

Having defined a linear order on the gates and on the nets, we are now ready to prove the theorem by induction on m (the number of nets).

**Induction hypothesis:** For every  $i \leq m'$  there exist:

- 1. a Boolean function  $f_{e_i}: \{0,1\}^k \to \{0,1\}$ , and

- 2. a propagation delay  $t_{pd}(e_i)$

such that the network  $e_i$  implements the Boolean function  $f_{e_i}$  with propagation delay  $t_{pd}(e_i)$ .

**Induction Basis:** We prove the induction basis for m' = k. Consider an  $i \leq k$ . Note that, for every  $i \leq k$ ,  $e_i$  is fed by the input gate  $v_i$ . Let  $x_i$  denote the output terminal of  $v_i$ . It follows that the digital signal along  $e_i$  always equals the digital signal  $x_i(t)$ . Hence we define  $f_{e_i}$  to be simply the projection on the *i*th component, namely  $f_{e_1}(\sigma_1, \ldots, \sigma_k) = \sigma_i$ . The propagation delay  $t_{pd}(e_i)$  is zero. The induction basis follows.

**Induction Step:** Assume that the induction hypothesis holds for m' < m. We wish to prove that it also holds for m' + 1. Consider the net  $e_{m'+1}$ . Let  $v_i$  denote the gate that feeds the net  $e_{m'+1}$ . To simplify notation, assume that the gate  $v_i$  has two terminals that are fed by the nets  $e_j$  and  $e_k$ , respectively. The ordering of the nets guarantees that  $j, k \leq m'$ . By the induction hypothesis, the net  $e_j$  (resp.,  $e_k$ ) implements a Boolean function  $f_{e_j}$  (resp.,  $f_{e_k}$ ) with propagation delay  $t_{pd}(e_j)$  (resp.,  $t_{pd}(e_k)$ ). This implies that both inputs to gate  $v_i$  are stable during the interval

$$[t_1 + \max\{t_{pd}(e_j), t_{pd}(e_k)\}, t_2].$$

Gate  $v_i$  implements a Boolean function  $f_{v_i}$  with propagation delay  $t_{pd}(v_i)$ . It follows that the output of gate  $v_i$  equals

$$f_{v_i}(f_{e_i}(\vec{x}(t)), f_{e_k}(\vec{x}(t)))$$

during the interval

$$[t_1 + \max\{t_{pd}(e_j), t_{pd}(e_k)\} + t_{pd}(v_i), t_2].$$

We define  $f_{e_{m'+1}}$  to be the Boolean function obtained by the composition of Boolean functions  $f_{e_{m'+1}}(\vec{\sigma}) = f_{v_i}(f_{e_j}(\vec{\sigma}), f_{e_k}(\vec{\sigma}))$ . We define  $t_{pd}(e_{m'+1})$  to be  $\max\{t_{pd}(e_j), t_{pd}(e_k)\} + t_{pd}(v_i)$ , and the induction step follows.

The digital abstraction allows us to assume that the signal corresponding to every net in a combinational circuit is logical (provided that the time that elapses since the inputs become stable is at least the propagation delay). This justifies the convention of identifying a net with the digital value of the net.

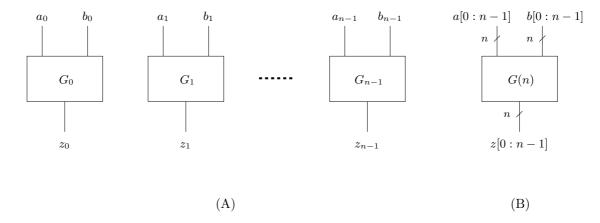

The proof of Theorem 2.1 leads to two related algorithms. One algorithm simulates a combinational circuit, namely, given a combinational circuit and a Boolean assignment to the inputs  $\vec{x}$ , the algorithm can compute the digital signal of every net after a sufficient amount of time elapses. The second algorithm computes the propagation delay of each net. Of particular interest are the nets that feed the output gates of the combinational circuit. Hence, we may regard a combinational circuit as a "macro-gate". All instances of the same combinational circuit implement the same Boolean function and have the same propagation delay.

The algorithms are very easy. For convenience we describe them as one joint algorithm. First, the directed graph DG(C) is constructed (this takes linear time). Then the gates are sorted in topological order (this also takes linear time). This order also induced an order on the nets. Now a sequence of *relaxation* steps take place for nets  $e_1, e_2, \ldots, e_m$ . In a relaxation step the propagation delay of a net  $e_i$  two computations take place:

1. The Boolean value of  $e_i$  is set to

$f_{v_j}(\vec{I}_{v_j}),$

where  $v_j$  is the gate that feeds the net  $e_i$  and  $\vec{I}_{v_j}$  is the binary vector that describes the values of the nets that feed gate  $v_j$ .

2. The propagation delay of the gate that feeds  $e_i$  is set to

$$t_{pd}(e_i) \leftarrow t_{pd}(v_j) + \max\{t_{pd}(e')\}_{\{e' \text{ feeds } v_i\}}.$$

If the number of outputs of each gate is constant, then the total amount of time spend in the relaxation steps is linear, and hence the running time of this algorithm is linear. (Note that the input length is the number of gates plus the sum of the sizes of the nets.)

**Question 2.3** Prove that the total amount of time spent in the relaxation steps is linear if the fan-in of each gate is constant (say, at most 3).

Note that it is not true that each relaxation step can be done in constant time if the fan-in of the gates is not constant. Can you still prove linear running time if the fan-in of the gates is not constant but the number of outputs of each gate is constant?

Can you suggest a slight weakening of this restriction which still maintains a linear running time?

## 2.5 Cost and propagation delay

In this section we define the cost and propagation delay of a combinational circuit.

We associate a cost with every gate. We denote the cost of a gate G by c(G).

**Definition 2.9** The cost of a combinational circuit  $C = \langle \mathcal{G}, \mathcal{N} \rangle$  is defined by

$$c(C) \stackrel{\scriptscriptstyle \triangle}{=} \sum_{G \in \mathcal{G}} c(G).$$

The following definition defined the propagation delay of a combinational circuit.

**Definition 2.10** The propagation delay of a combinational circuit  $C = \langle \mathcal{G}, \mathcal{N} \rangle$  is defined by

$$t_{pd}(C) \stackrel{\scriptscriptstyle \Delta}{=} \max_{N \in \mathcal{N}} t_{pd}(N).$$

We often refer to the propagation delay of a combinational circuit as its *depth* or simply its *delay*.

**Definition 2.11** A sequence  $p = \{v_0, v_1, \ldots, v_k\}$  of gates from  $\mathcal{G}$  is a path in a combinational circuit  $C = \langle \mathcal{G}, \mathcal{N} \rangle$  if p is a path in the directed graph DG(C).

The propagation delay of a path p is defined as

$$t_{pd}(p) = \sum_{v \in p} t_{pd}(v).$$

The proof of the following claim follows directly from the proof of Theorem 2.1.

**Claim 2.2** The propagation delay of a combinational circuit  $C = \langle \mathcal{G}, \mathcal{N} \rangle$  equals

$$t_{pd}(C) = \max_{paths \ p} t_{pd}(p)$$

Paths, the delay of which equals the propagation delay of the circuit, are called *critical paths*.

- **Question 2.4** 1. Describe a combinational circuit with n gates that has at least  $2^{n/2}$  paths. Can you describe a circuit with  $2^n$  different paths?

- 2. In Claim 2.2 the propagation delay of a combinational circuit is defined to be the maximum delay of a path in the circuit. The number of paths can be exponential in n. How can we compute the propagation delay of a combinational circuit in linear time?

Müller and Paul compiled the following costs and delays of gates. These figures were obtained by considering ASIC libraries of two technologies and normalizing them with respect to the cost and delay of an inverter. They referred to these figures as Motorola and Venus. Table 2.1 summarizes the normalized costs and delays in these technologies.

## 2.6 Syntax and semantics

In this chapter we have used both explicitly and implicitly the terms *syntax* and *semantics*. These terms are so fundamental that they deserve a section.

The term semantics (in our context) refers to the function that a circuit implements. Often, the semantics of a circuit is referred to as the *functionality* or even the *behavior* of the circuit. In general, the semantics of a circuit is a formal description that relates the outputs of the circuit to the inputs of the circuit. In the case of combinational circuits,

| Gate      | Motorola |       | Venus    |       |

|-----------|----------|-------|----------|-------|

|           | $\cos t$ | delay | $\cos t$ | delay |

| INV       | 1        | 1     | 1        | 1     |

| AND,OR    | 2        | 2     | 2        | 1     |

| NAND, NOR | 2        | 1     | 2        | 1     |

| XOR, NXOR | 4        | 2     | 6        | 2     |

| MUX       | 3        | 2     | 3        | 2     |

Table 2.1: Costs and delays of gates

semantics are described by Boolean functions. Note that in non-combinational circuits, the output depends not only on the current inputs, so semantics cannot be described simply by a Boolean function.

The term syntax refers to a formal set of rules that govern how "grammatically correct" circuits are constructed from smaller circuits (just as sentences are built of words). In the syntactic definition of combinational circuits the functionality (or gate-type) of each gate is not important. The only part that matters is that the rules for connecting gates together are followed. Following syntax in itself does not guarantee that the resulting circuit is useful. Following syntax is, in fact, a restriction that we are willing to accept so that we can enjoy the benefits of well defined functionality, simple simulation, and simple timing analysis. The restriction of following syntax rules is a reasonable choice since every Boolean function can be implemented by a syntactically correct combinational circuit.

## 2.7 Summary

Combinational circuits were formally defined in this chapter. We started by considering the basic building blocks: gates and wires. Gates are simply implementations of Boolean functions. The digital abstraction enables a simple definition of what it means to implement a Boolean function f. Given a propagation delay  $t_{pd}$  and stable inputs whose digital value is  $\vec{x}$ , the digital values of the outputs of a gate equal  $f(\vec{x})$  after  $t_{pd}$  time elapses.

Wires are used to connect terminals together. Bunches of wires are used to connect multiple terminals to each other and are called nets. Simple nets are nets in which the direction in which information flows is well defined; from output terminals of gates to input terminals of gates.

The formal definition of combinational circuits turns out to be most useful. It is a syntactic definition that only depends on the topology of the circuit, namely, how the terminals of the gates are connected. One can check in linear time whether a given circuit is indeed a combinational circuit. Even though the definition ignores functionality, one can compute in linear time the digital signals of every net in the circuit. Moreover, one can also compute in linear time the propagation delay of every net.

Two quality measures are defined for every combinational circuit: cost and propagation delay. The cost of a combinational circuit is the sum of the costs of the gates in the circuit. The propagation delay of a combinational is the maximum delay of a path in the circuit.

## Chapter 3

## Trees

In this chapter we deal with combinational circuits that have a topology of a tree. We begin by considering circuits for associative Boolean function. We then prove two lower bounds; one for cost and one for delay. These lower bounds do not assume that the circuits are trees. The lower bounds prove that trees have optimal cost and balanced trees have optimal delay.

## 3.1 Trees of associative Boolean gates

In this section, we deal with combinational circuits that have a topology of a tree. All the gates in the circuits we consider are instances of the same gate that implements an associative Boolean function.

#### 3.1.1 Associative Boolean functions

**Definition 3.1** A Boolean function  $f: \{0,1\}^2 \rightarrow \{0,1\}$  is associative if

$$f(f(\sigma_1, \sigma_2), \sigma_3) = f(\sigma_1, f(\sigma_2, \sigma_3)),$$

for every  $\sigma_1, \sigma_2, \sigma_3 \in \{0, 1\}$ .

**Question 3.1** List all the associative Boolean functions  $f: \{0, 1\}^2 \rightarrow \{0, 1\}$ .

A Boolean function defined over the domain  $\{0,1\}^2$  is often denoted by a dyadic operator, say  $\odot$ . Namely,  $f(\sigma_1, \sigma_2)$  is denoted by  $\sigma_1 \odot \sigma_2$ . Associativity of a Boolean function  $\odot$  is then formulated by

$$\forall \sigma_1, \sigma_2, \sigma_3 \in \{0, 1\} : (\sigma_1 \odot \sigma_2) \odot \sigma_3 = \sigma_1 \odot (\sigma_2 \odot \sigma_3).$$

This implies that one may omit parenthesis from expressions involving an associative Boolean function and simply write  $\sigma_1 \odot \sigma_2 \odot \sigma_3$ . Thus we obtain a function defined over  $\{0, 1\}^n$  from a dyadic Boolean function. We formalize this composition of functions as follows.

**Definition 3.2** Let  $f : \{0,1\}^2 \to \{0,1\}$  denote a Boolean function. The function  $f_n : \{0,1\}^n \to \{0,1\}$ , for  $n \ge 2$  is defined by induction as follows.

- 1. If n = 2 then  $f_2 \equiv f$  (the sign  $\equiv$  is used instead of equality to emphasize equality of functions).

- 2. If n > 2, then  $f_n$  is defined based on  $f_{n-1}$  as follows:

$f_n(x_1, x_2, \dots, x_n) \stackrel{\scriptscriptstyle \triangle}{=} f(f_{n-1}(x_1, \dots, x_{n-1}), x_n).$

If  $f(x_1, x_2)$  is an associative Boolean function, then one could define  $f_n$  in many equivalent ways, as summarized in the following claim.

**Claim 3.1** If  $f: \{0,1\}^2 \to \{0,1\}$  is an associative Boolean function, then

$f_n(x_1, x_2, \dots, x_n) = f(f_k(x_1, \dots, x_k), f_{n-k}(x_{k+1}, \dots, x_n)),$

for every  $k \in [2, n-2]$ .

**Question 3.2** Show that the set of functions  $f_n(x_1, \ldots, x_n)$  that are induced by associative Boolean functions  $f: \{0, 1\}^2 \to \{0, 1\}$  is

```

\{ constant 0, constant 1, x_1, x_n, AND, OR, XOR, NXOR \}.

```

The implication of Question 3.2 is that there are only four non-trivial functions  $f_n$  (which?). In the rest of this section we will only consider the Boolean function OR. The discussion for the other three non-trivial functions is analogous.

#### 3.1.2 OR-trees

**Definition 3.3** A combinational circuit  $C = \langle \mathcal{G}, \mathcal{N} \rangle$  that satisfies the following conditions is called an OR-tree(n).

- 1. Input: x[n-1:0].

- 2. **Output:**  $y \in \{0, 1\}$

- 3. **Functionality:**  $y = OR(x[0], x[1], \dots, x[n-1]).$

- 4. Gates: All the gates in  $\mathcal{G}$  are OR-gates.

- 5. **Topology:** The underlying graph of DG(C) (i.e. undirected graph obtained by ignoring edge directions) is a rooted binary tree.

Consider the binary tree T corresponding to the underlying graph of DG(C), where C is an OR-tree(n). The root of T corresponds to the output gate of C. The leaves of T correspond to the input gates of C, and the interior nodes in T correspond to OR-gates in C.

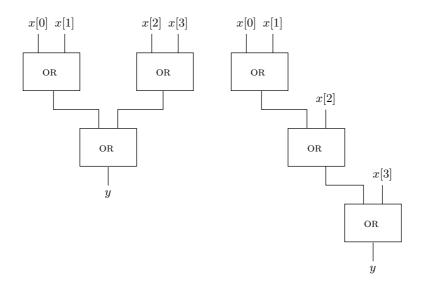

Claim 3.1 provides a "recipe" for implementing an OR-tree using OR-gates. Consider a rooted binary tree with n leaves. The inputs are fed via the leaves, an OR-gate is positioned in every node of the tree, and the output is obtained at the root. Figure 3.1 depicts two OR-tree(n) for n = 4.

One could also define an OR-tree(n) recursively, as follows.

#### 3.1. TREES OF ASSOCIATIVE BOOLEAN GATES

Figure 3.1: Two implementations of an OR-tree(n) with n = 4 inputs.

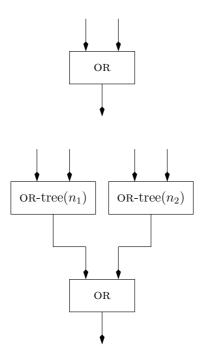

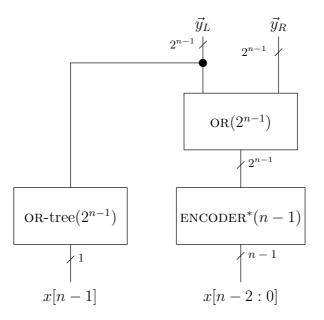

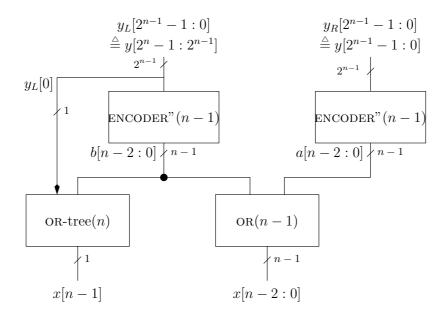

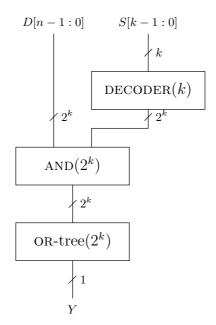

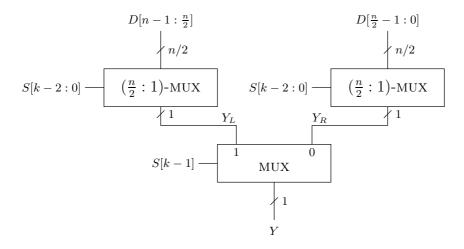

**Definition 3.4** An OR-tree(n) is defined recursively as follows (see Figure 3.2):

- 1. Basis: a single OR-gate is an OR-tree(2).

- 2. Step: an OR(n)-tree is a circuit in which

- (a) the output is computed by an OR-gate, and

- (b) the inputs of this OR-gate are the outputs of OR-tree $(n_1)$  & OR-tree $(n_2)$ , where  $n = n_1 + n_2$ .

**Question 3.3** Design a zero-tester defined as follows.

**Input:** x[n-1:0].

**Output:** y

#### **Functionality:**

y = 1 iff  $x[n-1:0] = 0^n$ .

- 1. Suggest a design based on an OR-tree.

- 2. Suggest a design based on an AND-tree.

- 3. What do you think about a design based on a tree of NOR-gates?

#### 3.1.3 Cost and delay analysis

You may have noticed that both OR-trees depicted in Figure 3.1 contain three OR-gates. However, their delay is different. The following claim summarizes the fact that all OR-trees have the same cost.

**Claim 3.2** The cost of every OR-tree(n) is  $(n-1) \cdot c(OR)$ .

Figure 3.2: A recursive definition of an OR-tree(n).

**Proof:** The proof is by induction on n. The induction basis, for n = 2, follows because OR-tree(2) contains a single OR-gate. We now prove the induction step.

Let C denote an OR-tree(n), and let g denote the OR-gate that outputs the output of C. The gate g is fed by two wires  $e_1$  and  $e_2$ . The recursive definition of OR-gate(n) implies the following. For i = 1, 2, the wire  $e_i$  is the output of  $C_i$ , where  $C_i$  is an OR-tree $(n_i)$ . Moreover,  $n_1 + n_2 = n$ . The induction hypothesis states that  $c(C_1) = (n_1 - 1) \cdot c(\text{OR})$  and  $c(C_2) = (n_2 - 1) \cdot c(\text{OR})$ . We conclude that

$$c(C) = c(g) + c(C_1) + c(C_2)$$

= (1 + n\_1 - 1 + n\_2 - 1) \cdot c(OR)

= (n - 1) \cdot c(OR),

and the claim follows.

The following question shows that the delay of an OR-tree(n) can be  $\lceil \log_2 n \rceil \cdot t_{pd}(OR)$ , if a balanced tree is used.

**Question 3.4** This question deals with different ways to construct balanced trees. The goal is to achieve a depth of  $\lceil \log_2 n \rceil$ .

- 1. Prove that if  $T_n$  is a rooted binary tree with n leaves, then the depth of  $T_n$  is at least  $\lceil \log_2 n \rceil$ .

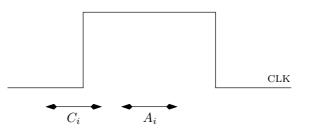

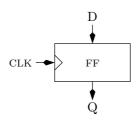

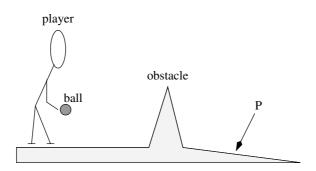

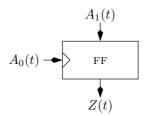

- 2. Assume that n is a power of 2. Prove that the depth of a complete binary tree with n leaves is  $\log_2 n$ .